|

| Three “accelerators on a chip” made of silicon are mounted on a clear base. Credit: SLAC National Accelerator Laboratory |

The Gordon and Betty Moore Foundation has awarded 13.5 million US dollars (12.6 million euros) to promote the development of a particle accelerator on a microchip. DESY and the University of Hamburg are among the partners involved in this international project, headed by Robert Byer of Stanford University (USA) and Peter Hommelhoff of the University of Erlangen-Nürnberg. Within five years, they hope to produce a working prototype of an “accelerator-on-a-chip”.

For decades, particle accelerators have been an indispensable tool in countless areas of research – from fundamental research in physics to examining the structure of biomolecules in order to develop new drugs. Accelerator-based research has repeatedly been awarded Nobel prizes. Until now, the necessary facilities have been very large and costly. Scientists and engineers are trying out a range of different approaches to build more compact and less expensive particle accelerators. For the time being, the big facilities will remain indispensable for many purposes, however there are some applications in which efficient miniature electron accelerators can provide completely new insights.

“The impact of shrinking accelerators can be compared to the evolution of computers that once occupied entire rooms and can now be worn around your wrist,” says Hommelhoff. This advance could mean that particle accelerators will become available in areas that have previously had no access to such technologies.

The aim of the project is to develop a new type of small, inexpensive particle accelerator for a wide range of different users. Apart from using the fast electrons themselves, they could also be used to produce high-intensity X-rays. “This prototype could set the stage for a new generation of ‘tabletop’ accelerators, with unanticipated discoveries in biology and materials science and potential applications in security scanning, medical therapy and X-ray imaging,” explains Byer.

|

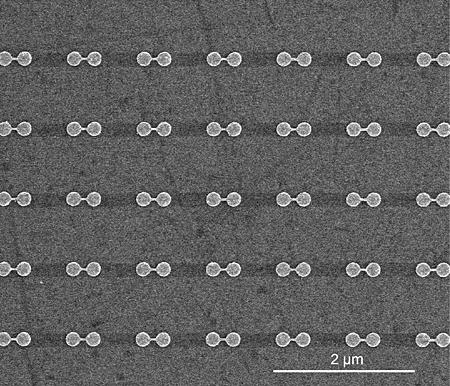

| Some of the accelerator-on-a-chip designs being explored by the international collaboration. Credit: SLAC National Accelerator Laboratory |

The project is based on advances in nano-photonics, the art of creating and using nano structures to generate and manipulate different kinds of light. A laser using visible or infrared light is used to accelerate the electrically charged elementary particles, rather than the radio-frequency (RF) waves currently used. The wavelength of this radiation is some ten to one hundred thousand times shorter than that of the radio waves, meaning that steeper accelerator gradients can be achieved than those using RF technology. “The advantage is that everything is up to fifty times smaller,” explains Franz Kärtner who is a Leading Scientist at DESY, as well as a professor at the University of Hamburg and the Massachusetts Institute of Technology (MIT) in the US, and a member of Hamburg’s Centre for Ultrafast Imaging (CUI), and who heads a similar project in Hamburg, funded by the European Research Council.

“The typical transverse dimensions of an accelerator cell shrink from ten centimetres to one micrometre,” adds Ingmar Hartl, head of the laser group in DESY’s Photon Science Division. At the moment, the material of choice for the miniature accelerator modules is silicon. “The advantage is that we can draw on the highly advanced production technologies that are already available for silicon microchips,” explains Hartl.

DESY will bring its vast knowhow as an internationally leader in laser technology to the project, which has already paid off in other collaborations involving the University of Erlangen-Nürnberg. There, Hommelhoff’s group showed that for slow electrons a micro-structured accelerator module is able to achieve steeper acceleration gradients than RF technology.

Byer’s group had demonstrated independently the same effect for fast, so-called relativistic electrons.

However, it is still a long way from an experimental set-up in a laboratory to a working prototype. Individual components of the system will have to be developed from scratch.

Among other things, DESY is working on a high-precision electron source to feed the elementary particles into the accelerator modules, a powerful laser for accelerating them, and an electron undulator for creating X-rays. In addition, the interaction between the miniature components is not yet a routine matter, especially not when it comes to joining up several accelerator modules.

The SINBAD (“Short Innovative Bunches and Accelerators at DESY”) accelerator lab that is currently being set up at DESY will provide the ideal testing environment for the miniature accelerator modules. “SINBAD will allow us to feed high-quality electron beams into the modules, to test the quality of the radiation and work out an efficient way of coupling the laser.

DESY offers unique opportunities in this respect,” explains Ralph Aßmann, Leading Scientist at DESY.

Apart from DESY, the Universities of Stanford, Erlangen-Nürnberg and Hamburg, SLAC National Accelerator Laboratory in the US, the Swiss Paul Scherrer Institute (PSI) and the University of California in Los Angeles (UCLA), the Purdue University, the Swiss Federal Institute of Technology in Lausanne (EPFL) and the Technical University of Darmstadt are also involved in the project, as well as the US company Tech-X.

The Gordon and Betty Moore Foundation fosters path-breaking scientific discovery, environmental conservation, patient care improvements and the preservation of the special character of the San Francisco Bay Area. Gordon Moore is one of the founders of the chip manufacturer Intel and the author of “Moore's Law”, which predicts that the number of transistors in an integrated circuit doubles approximately every two years.

DESY

Read on NTWA